Using GateMate 1 and 2 Bit Adders

The GateMate FPGA provides 1 and 2 bit adders, this article shows how to use them.

Dave Forhn created a game of life example to demonstrate their use, but his final solution used generic verilog, rather than explicitly using the 1 and 2 bit adders. This article explicitly uses the adders to increment the game of life.

The basic rule is that if a cell has 2 neighbours it stays the same, if it has 3 neighbours, it comes to life, and otherwise it dies. Basically we have to use the adders to count the neighbours of each cell.

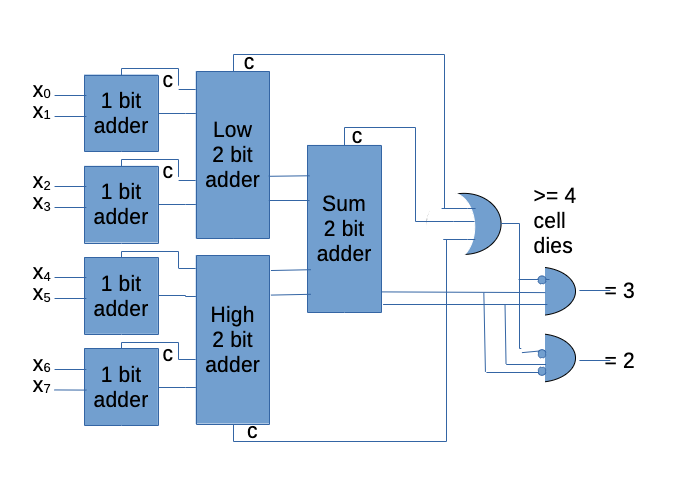

We can see this implemented in the following figure.

On the left hand column we add the individual bits using 1 bit adders. The output can be 0, 1 or 2, and so there are two bits output to the middle column. In the middle column we sum from two one bit adders. If either of those sums has a carry bit out, that is at least 4, and so the cell dies. Then in the third column, we sum the lower bits from the second column adders. If there is a carry bit, that is a 4, again the cell dies. All the 3 carry bits from the three bit adders are fed into the OR gatr at the top of the right hand column. If any of the carry bits are positive, that is a 4 and the cell dies. And that just leaves the two bottom and gates to tell if the final sum is a 3 or a 2. Of course if the carry bits indicated that it was over 4, it cannot be a 3 or a 2. So the ">=4 dies" OR gate is negated and fed into the 2 and 3 recognisers.

Built using the Forest Map Wiki